- WeeBit ReRAM memory fits into chips without changing the existing transistor structures

- Each ReRAM cell stores data using resistive switching, not traditional flash methods

- ReRAM can handle between 100,000 and 1 million write cycles

Texas Instruments’ decision to license embedded ReRAM from Weebit Nano has revived claims that flash memory has reached structural limits.

The deal follows earlier deals with SkyWater, DB HiTek and Onsemi, marking a steady escalation of production partners rather than an abrupt approval.

Weebit’s managing director, Coby Hanoch, told us All about circuits that the progression was deliberate, with each step increasing both the scale of the process and the credibility of the industry.

Architecture choices and manufacturing friction

“We went up an order of magnitude each time,” he said. “From SkyWater to DB HiTek to Onsemi and now to TI. Now we’re in the big league.”

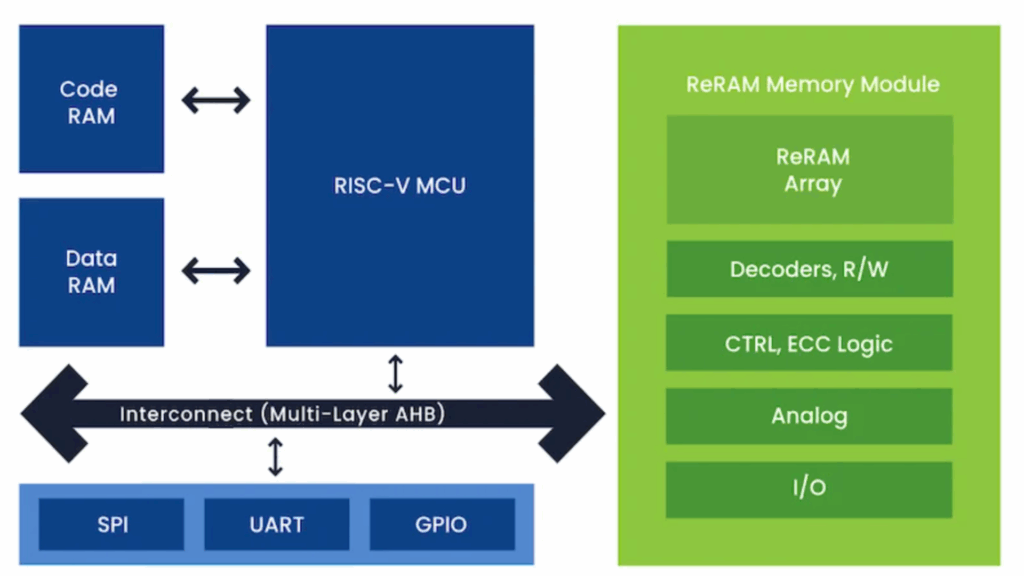

Weebit implements its ReRAM as a back-end-of-line module that allows integration without changing front-end transistor structures.

This approach keeps additional wafer costs close to 5% compared to much higher costs associated with embedded flash processes.

The memory cell itself relies on resistive switching instead of floating-gate storage, allowing bit-level access without block erase operations.

These design decisions are framed as pragmatic rather than revolutionary, relying on standard materials and conventional manufacturing tools.

“We said from day one that we would use standard materials, standard tools, standard flows,” he said. “We didn’t want to give fancy excuses for not working with us.”

From a specification standpoint, Weebit reports write speeds up to 100x faster than embedded flash along with endurance from 100,000 to 1 million cycles.

The company reports that power consumption is lower due to reduced operating voltages and direct access modes.

Its CEO bluntly claims that “power, speed, endurance, temperature and cost, on every axis that matters to embedded memory, ReRAM looks better than flash.”

The company also emphasizes immunity to electromagnetic interference, contrasting its technology with MRAM.

“We have seen cases where magnetic fields damaged MRAM in consumer environments,” Hanoch said, adding that major manufacturers found this risk unacceptable.

As process nodes shrink below 28nm, embedded flash becomes increasingly difficult to scale reliably.

Designers often compensate by pairing logic dies with external flash and staging data in SRAM at boot, increasing complexity and power consumption.

Hanoch claims that non-volatile ReRAM removes this inefficiency, enabling instant boot and tighter security margins.

The higher density of ReRAM compared to SRAM allows edge devices to store more data on chip, which directly improves computational accuracy.

“More bits on the same silicon means better accuracy for inference,” he said, while also pointing to demonstrated neuromorphic experiments where “the ReRAM bit behaves like a synapse.”

Weebit cites industry forecasts projecting ReRAM revenue to grow by about 45% per year, potentially reaching $1.7 billion within six years.

But its revenues remain modest, even as they rise, and the company attributes slower uptake to institutional caution rather than technical gaps.

“The biggest barrier is human nature,” Hanoch said, despite pointing to working silicon at multiple nodes and mass production qualifications.

Whether TI’s endorsement confirms that “ReRAM is the replacement for flash” remains to be seen.

Still, the search for a universal memory remains unresolved, with alternatives such as ULTRARAM, developed by Quinas Technology, entering the fray last year.

Follow TechRadar on Google News and add us as a preferred source to get our expert news, reviews and opinions in your feeds. Be sure to click the Follow button!

And of course you can too follow TechRadar on TikTok for news, reviews, video unboxings, and get regular updates from us on WhatsApp also.